# **TF112**

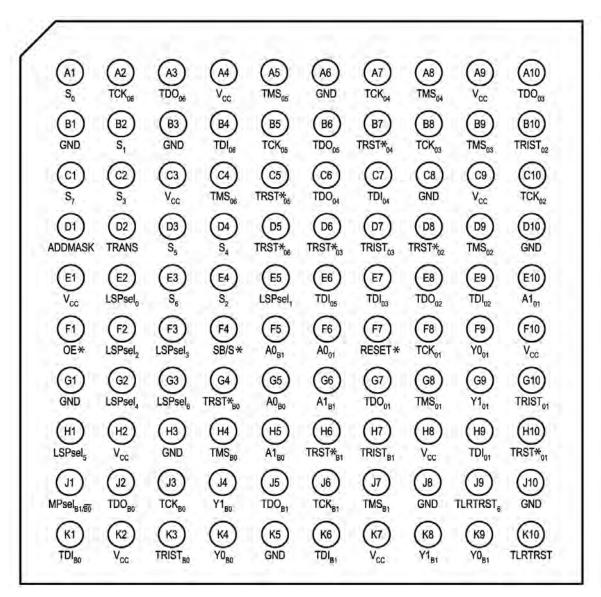

7 Port Multidrop IEEE 1149.1 (JTAG) Multiplexer

#### **Features**

- ATPG support from all major vendors

- Fully pin and function compatible with NSC SCANSTA112

- Muxes 7 local JTAG ports from 1 source

- Supports multidrop addressing

- Backplane Port and LSP0 can act as slave/master for multi-master operation

- Supports live insertion

- Transparent Mode for simplified FPGA/CPLD programming

- Pass-thru bits can be driven by pins or internal registers to assist Flash Programming

## Description

The TF112 combines a 7 port IEEE1149.1 (JTAG) multiplexer with addressable multi-drop capability. As a multiplexer, 7 local ports allow partitioning of scan chains to simplify and accelerate programming and test and debug sequences. Optional daughter cards or ICs are easily handled with dedicated scan chains. Local chains can be selected individually or in combination as required.

Addressable multi-drop capability allows operation on a backplane with other TF112s or similar addressable devices. 8 address pins are used to set the unique device address. Addressing the device is accomplished by loading the instruction register with a value matching the address pins. The backplane port and one of the local ports are bi-directional and may be set as master or slave. This feature enables multi-master operation.

All major ATPG vendors support this function and both addressing and selection of local ports is handled automatically by the vector generation software.

Muxing multiple Scan Chains

System Level JTAG Test and Programming

Multidrop and Hierarchical Scan Path Management

**Applications**

## **Function Diagrams**

## **Ordering Information**

|             |          |       | Ye    | ar Year Week Week       |

|-------------|----------|-------|-------|-------------------------|

| PART NUMBER | PACKAGE  | PACK  | / Qty | MARK                    |

| TF112-BBV   | BGA-100  | Tray, | 240   | YYWW<br>TF112<br>Lot ID |

| TF112-PBV   | TQFP-100 | Tray, | 90    | YYWW<br>TF112<br>Lot ID |

www.telefunkensemiconductors.com

## **Block Diagram**

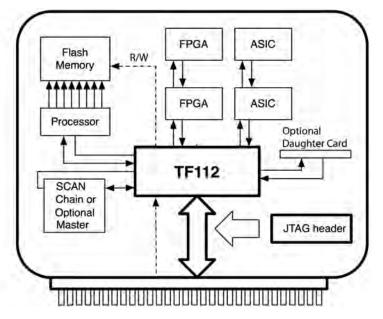

Figure 1. TF112 Block Diagram

#### **Overview**

Since its introduction in 1990, the IEEE1149.1 standard (JTAG) has become pervasive in complex digital hardware. In addition to structural test, the standard is now used extensively for tasks such as programming and emulation. These additional uses, along with the increase in complexity and pincount of FPGAs and ASICs, requires effective partitioning of scan chains to minimize test and programming time. The use of scan path multiplexers such as the TF112, enable the configuration of scan chains in an optimal manner. The seven local scan ports (LSPs) also provide a convenient way to provide scan access to optional daughter cards or ASICs. JTAG is also used in

fielded platforms for in-situ test and programming. System level JTAG requires the ability to address cards in a multidrop environment and this is accomplished using the de facto industry standard SCAN Bridge addressing scheme. Devices such as the TF112 are completely compatible on a multidrop backplane with other devices using the same scheme.

Addressing TF112 devices and the vector sequence required to select LSPs is an automated process and handled by commercial ATPG software products.

#### Architecture

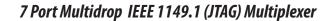

A basic block diagram of the TF112 is shown in Figure 2. The functional blocks are as follows:

The TDI/TDO Crossover Master Slave Logic defines the bidirectional B0 and B1 ports as Master and Slave as controlled by MPsel.

The Selection Control Block compares the device address as set by pins S0 thru S7, with the address entered into the instruction register and determines if the TF112 is selected. A selected device is then ready for further instructions; nonselected devices remain in standby. The TAP Controller is the IEEE1149.1 standard Test Access Port. This 16 state-machine controls the instructions, functionality and timing relationships as defined by the standard.

7 Port Multidrop IEEE 1149.1 (JTAG) Multiplexer

The Local Scan Port Network is the primary multiplexer that selects individual or combinations of local scan ports. Each local port includes the complete 5 pin boundary scan signal suite.

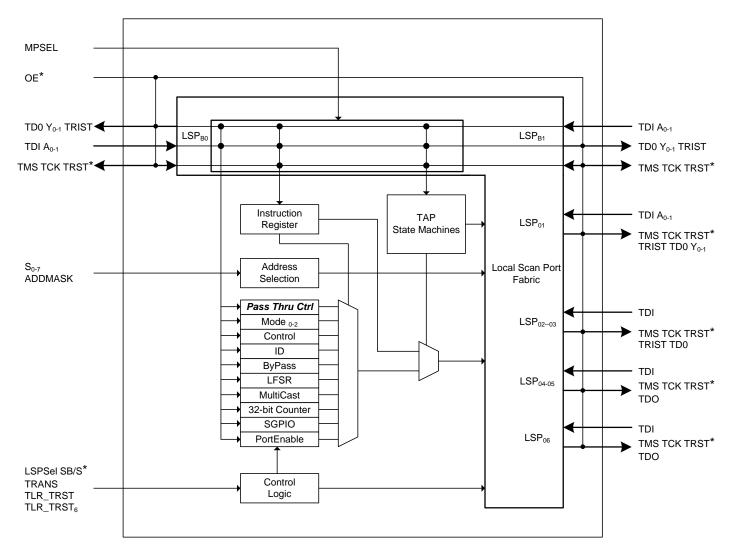

#### **BGA Connection Diagram**

Figure 2. BGA Top View

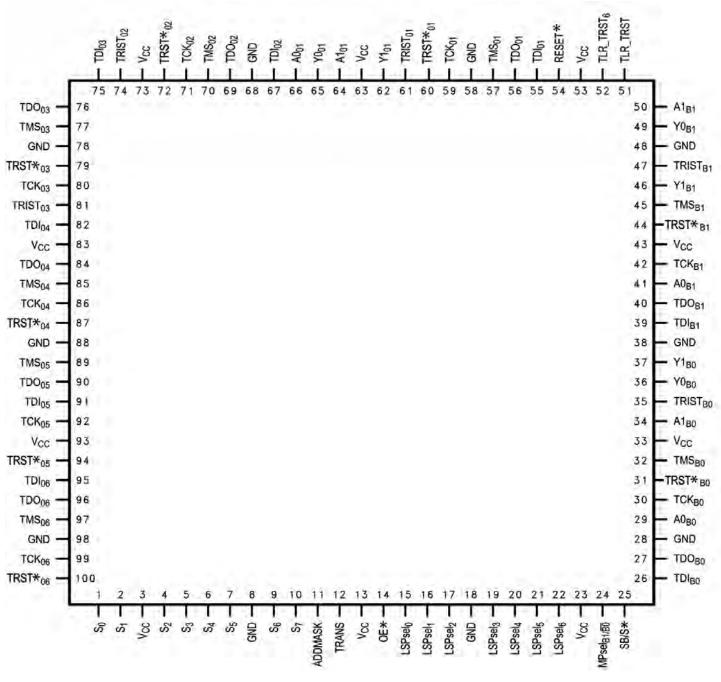

#### **TQFP** Connection Diagram

Figure 3. TQFP Top View

## **Pin Description**

## 7 Port Multidrop IEEE 1149.1 (JTAG) Multiplexer

| Pin Name                                | No.<br>Pins | I/O | Description                                                                                                                                                                                                                                                                          |  |

|-----------------------------------------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCC                                     | 10          | N/A | Power                                                                                                                                                                                                                                                                                |  |

| GND                                     | 10          | N/A | Ground                                                                                                                                                                                                                                                                               |  |

| RESET*                                  | 1           | I   | Forces an asynchronous reset of the device                                                                                                                                                                                                                                           |  |

| ADDMASK                                 | 1           | Ι   | When asserted, address pins S6 and S7 are masked. This feature is intended for applications where it is desirable for a local master to use the smaller address space and the full address is used at the system level.                                                              |  |

| MP <sub>sel</sub>                       | 1           | I   | Master Port Selection. Determines if $LSP_{B0}$ or $LSP_{B1}$ is the Master port. The non-selected port becomes $LSP_{00}$ . A logic LOW selects $LSP_{B0}$ as master Port                                                                                                           |  |

| SB/S*                                   | 1           | I   | Selects ScanBridge (logic HIGH) or Stitcher Mode (logic LOW)                                                                                                                                                                                                                         |  |

| LSP <sub>sel(0-6)</sub>                 | 7           | I   | In stitcher mode, these pins select LSPs for inclusion in the Scan chain.                                                                                                                                                                                                            |  |

| TRANS                                   | 1           | I   | When the TF112 is to be used in the Stitcher configuration, setting the TRANS pin<br>with a logic HIGH will place the device in Transparent Mode. Transparent mode<br>eliminates the registers and pad bits in the scan chain providing a simpler but<br>generally slower scan path. |  |

| TLR_TRST                                | 1           | I   | This pin can be used to set the TRST* value of LSPs (0-5) over-riding the machine logic. This feature is included to accommodate non-com IEEE1149.1 devices where TRST* must remain HIGH.                                                                                            |  |

| TLR_TRST <sub>6</sub>                   | 1           | Ι   | This pin can be used to set the TRST* value of LSP6 over-riding the state machine logic. This feature is included to accommodate non-compliant IEEE1149.1 devices where TRST must remain HIGH.                                                                                       |  |

| TDI <sub>B0</sub> TDI <sub>B1</sub>     | 2           | I   | This is the Master Test Data Input as described by IEEE1149.1 and includes a 25K ohm internal pull-up. MPsel determines if port B0 or B1 is the master with the non-selected port becoming LSP0. When the device is powered-down this pin is high impedance.                         |  |

| TMS <sub>BO</sub> TMS <sub>B1</sub>     | 2           | I/O | This is the Master Test Mode Select as described by IEEE1149.1. The input includes a 25K ohm internal pull-up. MPsel determines if port B0 or B1 is the master with the non-selected port becoming LSP0. When the device is powered-down this pin is high impedance.                 |  |

| TDO <sub>B0</sub> TDO <sub>B1</sub>     | 2           | 0   | This is the Master Test Data Output as described by IEEE1149.1 and has 12 mA drive current. MPsel determines if port B0 or B1 is the master with the non-selected port becoming $LSP_0$ . When the device is powered-down this pin is high impedance.                                |  |

| TCK <sub>B0</sub> TCK <sub>B1</sub>     | 2           | I/O | This is the Master Test Clock as described by IEEE1149.1. MPsel determines if port B0 or B1 is the master with the non-selected port becoming LSP <sub>0</sub> . When the device is powered-down this pin is high impedance.                                                         |  |

| TRST* <sub>B0</sub> TRST* <sub>B1</sub> | 2           | I/O | This is the Master Test Reset as described by IEEE1149.1. MPsel determines if port B0 or B1 is the master with the non-selected port becoming $LSP_0$ . When the device is powered-down this pin is high impedance                                                                   |  |

## Pin Description (Continued)

| Pin Name                                                            | No.<br>Pins | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y0 <sub>80</sub> Y1 <sub>80</sub> Y0 <sub>81</sub> Y1 <sub>81</sub> | 4           | 0   | Master Pass-through Outputs. General purpose outputs which are driven by the corresponding input of the selected LSP. (not available when multiple LSPs are selected). There is also an override instruction available in which case the outputs of LSP <sub>0</sub> are controlled by the contents of an internal register. These outputs have 12 mA current drive. MPsel determines if port B0 or B1 is the master with the non-selected port becoming LSP <sub>0</sub> . |

| $AO_{B0}A1_{B0}AO_{B1}A1_{B1}$                                      | 4           | I   | Master Pass-through Inputs. General purpose inputs which are driven to the Yn outputs of the selected LSP. (not available when multiple LSPs are selected). These pins include 25K ohm pull-up resistors. MPsel determines if port B0 or B1 is the master with the non-selected port becoming the LSP <sub>0</sub>                                                                                                                                                          |

| TRIST <sub>B0</sub> TRIST <sub>B1</sub> TRIST <sub>(1-3)</sub>      | 5           | 0   | This signal is asserted high when the corresponding TDO is high-impedance.<br>This feature is included to support alternative physical layers where TRIST would<br>enable/disable an external translator                                                                                                                                                                                                                                                                    |

| S <sub>(0-7)</sub>                                                  | 8           | I   | These 8 inputs set the TF112 address used for addressing in a multidrop environment                                                                                                                                                                                                                                                                                                                                                                                         |

| OE*                                                                 | 1           | Ι   | When HIGH this control signal sets the LSPs in high-impedance. This feature enables the LSPs to be driven by an alternate resource.                                                                                                                                                                                                                                                                                                                                         |

| TDO <sub>(1-6)</sub>                                                | 6           | 0   | Test Data Out as defined by IEEE1149.1 for each of the LSPs. These outputs have 12 mA drive.                                                                                                                                                                                                                                                                                                                                                                                |

| TDI <sub>(1-6)</sub>                                                | 6           | l   | Test Data In as defined by IEEE1149.1 for each of the LSPs. These inputs have a 25K ohm internal pull-up.                                                                                                                                                                                                                                                                                                                                                                   |

| TMS <sub>(1-6)</sub>                                                | 6           | 0   | Test Mode Select as defined by IEEE1149.1 for each of the LSPs. These outputs have 24mA of drive current.                                                                                                                                                                                                                                                                                                                                                                   |

| TCK <sub>(1-6)</sub>                                                | 6           | 0   | Test Clock as defined by IEEE1149.1 for each of the LSPs. These outputs have 24mA of drive current.                                                                                                                                                                                                                                                                                                                                                                         |

| TRST* <sub>(1-6)</sub>                                              | 6           | 0   | Test Reset as defined in IEEE1149.1 for each of the LSPs. These outputs have 24mA of drive current.                                                                                                                                                                                                                                                                                                                                                                         |

| A0 <sub>0</sub> ,A1 <sub>1</sub>                                    | 2           | I   | Local Pass-through Inputs. General purpose inputs which are driven to the corresponding master Yn output. (not available when multiple LSPs are selected). These pins include 25K ohm pull-up resistors.                                                                                                                                                                                                                                                                    |

| Y0 <sub>1</sub> Y1 <sub>1</sub>                                     | 2           | 0   | Local Pass-through Outputs. General purpose outputs which are driven by the corresponding A1 input of the selected Master. There is also an override instruction available in which case the outputs of LSP1 are controlled by the contents of an internal register. (not available when multiple LSPs are selected). These outputs have 12 mA current drive.                                                                                                               |

#### **Application Overview**

The IEEE1149.1 (JTAG) standard has become pervasive in complex digital systems and used for a variety of tasks. The TF112 is a flexible and configurable device enabling efficient and cost effective implementation of JTAG for test, programming and debug. A critical element of cost effective JTAG is the use of software tools for Auto-Test-Pattern-Generation (ATPG) and diagnostics. The TF112 architecture is an established industry de facto standard and supported by all major ATPG engines. Essential elements of the device operation such as addressing and selection of Local Scan Ports (LSPs) is handled in ATPG. Thus only a general knowledge of the device function is necessary, the specific addressing and LSP selection protocol is handled by the software tools.

The IEEE1149.1 standard describes a serial chain encompassing as many devices as required. However in complex systems a single serial chain is grossly inadequate and inefficient. The TF112 includes two methods of creating multiple chains, those being addressability and scan path muxing. The TF112 only responds to its specific address and the 8 external address bits provide 249 unique addresses, along with several multicast addresses. Multidrop addressing is generally used in backplanes where a TF112 on each card is given a unique address. Each card can then be individually accessed by embedded or external JTAG masters. In addition to multidrop addressing, the TF112 is also a scan path mux supporting up to 7 individual chains or LSPs. (Local-Scan-Ports) Typically the multidrop addressing is used to access a specific card and then the mux functionality used to support multiple chains on a card.

The TF112 has two operational modes, those being "SCANBridge" mode, typically supported by ATPG, and "Stitcher" mode, where device functionality is established by external pins. Stitcher mode is often useful in a lab or development setting where ATPG tools and vectors may not yet be available.

The TF112 support both individual addressing and broadcast/ multicast addressing operations. During individual addressing operation the master's port  $TDO_{Bn}$  is active. During broadcast/ multicast addressing operations the master's port  $TDO_{Bn}$  is inactive.

#### ScanBridge Mode

In ScanBridge mode device addressing and LSP selection are typically handled automatically using ATPG tools. ScanBridge mode uses pad bits and internal registers and thus generally provides the fastest test and programming capability.

#### 7 Port Multidrop IEEE 1149.1 (JTAG) Multiplexer Transparent Mode

IEEE1149.1 is a synchronous serial vector set. To optimize timing relationships and thus support higher TCK clock rates, the TF112 when in normal operation, inserts pad bits in the scan path. These additional bits are accounted for in the ATPG vector sets and therefore not observed by the user, provided a major commercial ATPG package is generating the vectors. In instances where ATPG is not used it may be desirable to remove these additional bits and simply buffer the IEEE1149.1 signals from the master port to the selected LSP(s). This is known as Transparent mode and is available in ScanBridge mode via an instruction and Stitcher mode using the TRANS pin.

#### **Multiple Master**

The TF112 includes a multi-master capability where the master port can be either B0 or B1 with the non-master port then becoming LSP0. This feature is controlled by the MPsel pin and is included to assist with multimaster operation where vectors may be imported over the backplane, from a local embedded master or thru an external source such as ATE.

#### **Pass-Thru Bits**

Pass-thru bits are provided to assist with tasks such as Flash programming where external control of Read/Write may be desired. The TF112 pass-thru outputs are driven by the corresponding Master input port unless the Override instruction (0xBF) is loaded, in which case the outputs are controlled by the contents of a register. Upon a POR or TRST, the Enable and Data bits will be set to the default, logic 0. If the Enable is then set to a logic 1, then the Pass-thru output will be controlled by the corresponding register value.

| Bit | Default | Function                           |  |  |  |

|-----|---------|------------------------------------|--|--|--|

| 0   | 0       | LSP0 Y <sub>0</sub> Data bit       |  |  |  |

| 1   | 0       | Enable LSP0 $Y_0$ as GPIO          |  |  |  |

| 2   | 0       | LSP0 Y <sub>1</sub> Data bit       |  |  |  |

| 3   | 0       | Enable LSP0 Y <sub>1</sub> as GPIO |  |  |  |

| 4   | 0       | LSP1 Y₀ Data bit                   |  |  |  |

| 5   | 0       | Enable LSP1 Y <sub>0</sub> as GPIO |  |  |  |

| 6   | 0       | LSP1 Y <sub>1</sub> Data bit       |  |  |  |

| 7   | 0       | Enable LSP1 Y <sub>1</sub> as GPIO |  |  |  |

Table 1. Pass-Thru Bit Data Register

## Absolute Maximum Ratings<sup>NOTE(1)</sup>

| Supply Voltage(V <sub>cc</sub> )                 | 0.3V to +4.0V  |

|--------------------------------------------------|----------------|

| IDC Input Diode Current (I <sub>IK</sub> )       |                |

| V <sub>I</sub> = -0.5V                           | 20 mA          |

| DC Input Voltage (V <sub>1</sub> )               | 0.5V to +3.9V  |

| DC Output Diode Current ( I <sub>ok</sub> )      |                |

| V <sub>o</sub> = -0.5V                           | 20mA           |

| DC Output Voltage (V <sub>o</sub> )              | 0.3V to +3.9V  |

| DC Output Source /Sink Current (I <sub>0</sub> ) | <u>+</u> 50mA  |

| DC Vcc or Ground Current                         | <u>+</u> 50mA  |

| per output Pin                                   |                |

| DC Latchup Source or Sink Current                | <u>+</u> 300mA |

| Junction Temperature (Plastic)                   | +150°C         |

| Storage Temperature                              | 65°C to +150°C |

|                                                  |                |

| Lead Temperature (Solder, 5 sec)<br>100L BGA<br>100L TQFP<br>Max Package Power Capacity @25°C |            |

|-----------------------------------------------------------------------------------------------|------------|

| 100L FBGA                                                                                     |            |

| 100L TQFP                                                                                     |            |

| Thermal Resistance ( $\theta_{JA}$ )                                                          |            |

| 100L FBGA                                                                                     | 35°C/W     |

| 100L TQFP                                                                                     | 59.1°C/W   |

| Package Derating above +25°C                                                                  |            |

| 100L FBGA                                                                                     |            |

| 100L TQFP                                                                                     | 16.92mW/°C |

| ESD Ratings                                                                                   |            |

| HBM <sup>NOTE(1)</sup>                                                                        | 4 KV       |

| MM <sup>NOTE(2)</sup>                                                                         | 250V       |

| CDM <sup>N07E(3)</sup>                                                                        | 1.25 KV    |

|                                                                                               |            |

NOTE(1) Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NOTE(1) Human Body Model, applicable standard JESD22-A114-C

NOTE(2) Machine Model, applicable standard JESD22-A115-A

NOTE(3) Field Induced Charge Device Model, applicable standard JESD22-C101-C

## **Recommended Operating Conditions**

| Symbol          | Parameter             | Pins            | MIN | ТҮР | MAX             | Unit |

|-----------------|-----------------------|-----------------|-----|-----|-----------------|------|

| V <sub>cc</sub> | Supply Voltage        | V <sub>cc</sub> | 3.0 |     | 3.6             | V    |

| V <sub>I</sub>  | Input Voltage         | V <sub>I</sub>  | 0   |     | V <sub>cc</sub> | V    |

| V <sub>o</sub>  | Output Voltage        | V <sub>o</sub>  | 0   |     | V <sub>cc</sub> | V    |

| T <sub>A</sub>  | Operating Temperature | All             | -40 |     | 85              | °C   |

## **DC Electrical Characteristics**

|                     |                        |                          | ges unless otherwise specified. |

|---------------------|------------------------|--------------------------|---------------------------------|

| Uver recommended of | oerating supply volta  | ade and temperature ran  | nes liniess otherwise sherifien |

|                     | peraining suppry voica | ige and temperature rain | ges amess otherwise specifica.  |

|                     |                        |                          |                                 |

| Symbol           | Parameter                                                                                                                                                                                                                                                                              | Conditions                                                      | MIN        | ΤΥΡ | MAX          | Unit |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------|-----|--------------|------|

| V <sub>IH</sub>  | Minimum high input voltage                                                                                                                                                                                                                                                             |                                                                 | 2.0        |     |              | V    |

| V <sub>IL</sub>  | Maximum Low input voltage                                                                                                                                                                                                                                                              |                                                                 |            |     | 0.8          | V    |

| V <sub>oH</sub>  | Minimum high output voltage<br>All outputs and I/O pins                                                                                                                                                                                                                                | $I_{out}$ =-100 $\mu A$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$ | VCC - 0.2V |     |              | V    |

| V <sub>oH</sub>  | $\begin{array}{c} \mbox{Minimum high output voltage} \\ \mbox{TDO}_{B0,}\mbox{TDO}_{B1,}\mbox{TRIST}_{B0,}\mbox{TRIST}_{B1,}\mbox{YO}_{B0,} \\ \mbox{Y1}_{B0,}\mbox{YO}_{B1,}\mbox{Y1}_{B1,}\mbox{TDO}_{(01-06),} \\ \mbox{YO}_{01,}\mbox{Y1}_{01,}\mbox{TRIST}_{(01-03)} \end{array}$ | I <sub>out</sub> = -12 mA<br>All outputs loaded                 | 2.4        |     |              | V    |

| V <sub>oH</sub>  | $\begin{array}{l} \mbox{Minimum high output voltage} \\ \mbox{TMS}_{BO,}\mbox{TMS}_{B1,}\mbox{TCK}_{BO,}\mbox{TCK}_{B1,}\mbox{TRST}^*_{B0,} \\ \mbox{TRST}^*_{B1,}\mbox{TMS}_{(01-06)} \\ \mbox{TCK}_{(01-06),}\mbox{TRST}^*_{(01-06),} \end{array}$                                   | I <sub>out</sub> = -24 mA                                       | 2.2        |     |              | v    |

| V <sub>ol</sub>  | Maximum low output voltage<br>All outputs and I/O pins                                                                                                                                                                                                                                 | $I_{out} = +100 \ \mu A$ $V_{IN} = V_{IH} \text{ or } V_{IL}$   |            |     | 0.2          | V    |

| V <sub>ol</sub>  | $\begin{array}{l} \mbox{Maximum low output voltage} \\ \mbox{TDO}_{B0,}\mbox{TDO}_{B1,}\mbox{TRIST}_{B0,}\mbox{TRIST}_{B1,}\mbox{YO}_{B0,} \\ \mbox{Y1}_{B0,}\mbox{YO}_{B1,}\mbox{Y1}_{B1,}\mbox{TDO}_{(01-06),} \\ \mbox{YO}_{01,}\mbox{Y1}_{01,}\mbox{TRIST}_{(01-03)} \end{array}$  | $I_{out} = +12 \text{ mA}$                                      |            |     | 0.4          |      |

| V <sub>ol</sub>  | $\begin{array}{c} \mbox{Maximum low output voltage} \\ \mbox{TMS}_{BO,}\mbox{TMS}_{B1,}\mbox{TCK}_{BO,}\mbox{TCK}_{B1,}\mbox{TRST}^*_{B0,} \\ \mbox{TRST}^*_{B1,}\mbox{TMS}_{(01-06)} \\ \mbox{TCK}_{(01-06),}\mbox{TRST}^*_{(01-06),} \end{array}$                                    | I <sub>out</sub> = +24 mA                                       |            |     | 0.55         |      |

| V <sub>IKL</sub> | Maximum input clamp diode voltage                                                                                                                                                                                                                                                      | IIK = -18 mA                                                    |            |     | -1.2         | V    |

| I <sub>IN</sub>  | Maximum input leakage current<br>(non-resistor input pins)                                                                                                                                                                                                                             | $V_{IN} = V_{CC}$ or GND                                        |            |     | <u>+</u> 5.0 | μΑ   |

| I <sub>ILR</sub> | Input current Low<br>(input and I/O pins with pull-up<br>resistors: $TDI_{B1}$ , $TDI_{B0}$ , $TMS_{B0}$ , $TMS_{B1}$ ,<br>$TRST_{B0}$ , $TRST_{B1}^{*}$ , $AO_{B0}$ , $A1_{B0}$ , $AO_{B1}$ ,<br>$A1_{B1}$ , $TDI_{(01-06)}$ , $AO_{01}$ , $A1_{01}$ )                                | $V_{IN} = GND$                                                  | -25        |     | -200         | μΑ   |

| I <sub>m</sub>   | Input High Current<br>(Input and I/O pins with pull-up<br>resistors: $TDI_{B1}$ , $TDI_{B0}$ , $TMS_{B0}$ , $TMS_{B1}$ ,<br>$TRST^*_{B0}$ , $TRST^*_{B1}$ , $AO_{B0}$ , $A1_{B0}$ , $AO_{B1}$ ,<br>$A1_{B1}$ , $TDI_{(01-06)}$ , $AO_{01}$ , $A1_{01}$ )                               | $V_{IN} = V_{CC}$                                               |            |     | 5.0          | μΑ   |

| I <sub>off</sub> | Power-off Leakage Current<br>Outputs and I/O pins without pull-<br>up resistors                                                                                                                                                                                                        | $V_{cc} = 0V, V_{IN} = 3.6V$<br>(Note 3)                        |            |     | ±5.0         | μA   |

| oz               | Maximum TRI-STATE Leakage<br>Current Outputs and I/0 pins<br>without pull-up resistors                                                                                                                                                                                                 |                                                                 |            |     | <u>+</u> 5.0 | μΑ   |

| I <sub>cc</sub>  | Maximum Quiescent Supply<br>Current                                                                                                                                                                                                                                                    | $V_{IN} = V_{CC}$ or GND                                        |            |     | 3.8          | mA   |

| I <sub>CCD</sub> | Maximum Dynamic Supply<br>Current                                                                                                                                                                                                                                                      | $V_{IN} = V_{CC}$ or GND, Input,<br>Freq = 25MH <sub>z</sub>    |            |     | 68           | mA   |

## **AC Electrical Characteristics: Scan Bridge Mode**

Over recommended operating supply voltage and temperature ranges unless otherwise specified.  $RL = 500\Omega$  to GND, CL = 50pf to GND, TR/TF = 2.5ns, Vmeasure = VCC/2

| Symbol        | Parameter                                                                        | Conditions | MIN | ТҮР  | МАХ | Unit |

|---------------|----------------------------------------------------------------------------------|------------|-----|------|-----|------|

| tPHL,<br>tPLH | Progpagation Delay $TCK_{B0}$ to $TDO_{B0}$ or $TDO_{B1}$                        |            |     | 8.5  |     | ns   |

| tPHL,<br>tPLH | Propagation Delay<br>TCK <sub>81</sub> to TDO <sub>80</sub> or TDO <sub>81</sub> |            |     | 8.5  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay<br>TCK <sub>B0</sub> to TDO <sub>(01-06)</sub>                 |            |     | 7.5  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay<br>TCK <sub>81</sub> to TDO <sub>(01-06)</sub>                 |            |     | 7.5  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay<br>TMS <sub>B0</sub> to TMS <sub>B1</sub>                      |            |     | 8.0  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay<br>TMS <sub>B1</sub> to TMS <sub>B0</sub>                      |            |     | 8.0  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay $TMS_{B0}$ to $TMS_{(01-6)}$                                   |            |     | 8.0  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay<br>TMS <sub>B1</sub> to TMS <sub>(01-6)</sub>                  |            |     | 8.0  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay $TCK_{B0}$ to $TCK_{B1}$                                       |            |     | 8.0  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay $TCK_{B1}$ to $TCK_{B0}$                                       |            |     | 8.0  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay $TCK_{B0}$ to $TCK_{(01-06)}$                                  |            |     | 7.5  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay $TCK_{B1}$ to $TCK_{(01-06)}$                                  |            |     | 7.5  |     | ns   |

| tPHL<br>tPLH  | Propagation Delay $TCK_{B0}$ to TRST* <sub>B1</sub>                              |            |     | 11.5 |     | ns   |

| tPHL<br>tPLH  | Propagation Delay $TCK_{B1}$ to $TRST^*_{B0}$                                    |            |     | 11.5 |     | ns   |

| tPHL<br>tPLH  | Propagation Delay $TCK_{B0}$ to $TRST^*_{(01-06)}$                               |            |     | 12.0 |     | ns   |

### AC Electrical Characteristics: Scan Bridge Mode (Continued)

Over recommended operating supply voltage and temperature ranges unless otherwise specified.

| Symbol       | Parameter                                                                               | Conditions | MIN | ТҮР | МАХ | Unit |

|--------------|-----------------------------------------------------------------------------------------|------------|-----|-----|-----|------|

| tPHL         | Propagation Delay<br>TCK <sub>Bn</sub> to TRIST <sub>BN</sub>                           |            |     | 8.5 |     | ns   |

| tPHL         | Propagation Delay<br>TCK <sub>Bn</sub> to TRIST <sub>(01-03</sub>                       |            |     | 8.0 |     | ns   |

| tPZL<br>tPZH | Propagation Delay TCK <sub>Bn</sub> to TDO <sub>(01-06)</sub> or TDO <sub>(01-06)</sub> |            |     | 9.0 |     | ns   |

| tPHL<br>tPLH | Propagation Delay<br>An to Yn                                                           |            |     | 6.0 |     | ns   |

## **AC Timing Characteristics: Scan Bridge Mode**

Over recommended operating supply voltage and temperature ranges unless otherwise specified.  $RL = 500\Omega$  to GND, CL = 50pf to GND, TR/TF = 2.5ns, Vmeasure = VCC/2

| Symbol           | Parameter                                                  | Conditions    | ТҮР  | Unit |

|------------------|------------------------------------------------------------|---------------|------|------|

| t <sub>s</sub>   | Setup time<br>TMS <sub>Bn</sub> to TCK <sub>Bn</sub>       |               | 2.5  | ns   |

| t <sub>H</sub>   | Hold Time<br>TMS <sub>Bn</sub> to TCK <sub>Bn</sub>        |               | 1.5  | ns   |

| t <sub>s</sub>   | Setup Time<br>TDI <sub>Bn</sub> to TCK <sub>Bn</sub>       |               | 3.0  | ns   |

| t <sub>H</sub>   | Hold Time<br>TDI <sub>Bn</sub> to TCK <sub>Bn</sub>        |               | 2.0  | ns   |

| t <sub>s</sub>   | Setup Time<br>TDI <sub>(01-06)</sub> to TCK <sub>Bn</sub>  |               | 1.0  | ns   |

| t <sub>H</sub>   | Hold Time<br>TDI <sub>(01-06)</sub> to TCK <sub>Bn</sub>   |               | 3.5  | ns   |

| t <sub>rec</sub> | Recovery Time<br>TCK <sub>Bn</sub> from TRST <sub>Bn</sub> |               | 1.0  | ns   |

| t <sub>w</sub>   | Clock Pulse Width<br>TCK <sub>Bn</sub> (H or L)            | tR/tF = 1.0ns | 10.0 | ns   |

| t <sub>w</sub> L | Reset Pulse Width<br>TRST* <sub>Bn</sub> (L)               | tR/tF = 1.0ns | 2.5  | ns   |

| F <sub>MAX</sub> | Maximum Clock Frequency (Note 6)                           | tR/tF = 1.0ns | 25   | ns   |

## **AC Electrical Characteristics: Stitcher Mode**

Over recommended operating supply voltage and temperature ranges unless otherwise specified.

| Parameter  | Conditions                                                                                                                     | ТҮР  | Units |

|------------|--------------------------------------------------------------------------------------------------------------------------------|------|-------|

| tPHL, tPLH | Propagation Delay $\text{TDI}_{B0}$ to $\text{TDO}_{B1}$ , $\text{TDI}_{B1}$ to $\text{TDO}_{B0}$                              | 12.5 | ns    |

| tPHL, tPLH | Propagation Delay $\text{TDI}_{B0}$ to $\text{TDO}_{01}$ , $\text{TDI}_{B1}$ to $\text{TDO}_{01}$                              | 12.5 | ns    |

| tPHL, tPLH | Propagation Delay TDI <sub>LSPn</sub> to TDO <sub>LSPn+1</sub>                                                                 | 12.5 | ns    |

| tPHL, tPLH | Propagation Delay $TMS_{B0}$ to $TMS_{B1}$ , $TMS_{B1}$ to $TMS_{B0}$                                                          | 12.5 | ns    |

| tPHL, tPLH | Propagation Delay TMS $_{B0}$ to TMS $_{(01-06)}$ , TMS $_{B1}$ to TMS $_{(01-06)}$                                            | 12.5 | ns    |

| tPHL, tPLH | Propagation Delay TRST $_{B0}^{\bullet}$ to TRST $_{B1,}^{\bullet}$ TRST $_{B1}^{\bullet}$ to TRST $_{B0}^{\bullet}$           | 12.5 | ns    |

| tPHL, tPLH | Propagation Delay TRST $_{B0}^{\bullet}$ to TRST $_{(01-06),}^{\bullet}$ TRST $_{B1}^{\bullet}$ to TRST $_{(01-06)}^{\bullet}$ | 12.5 | ns    |

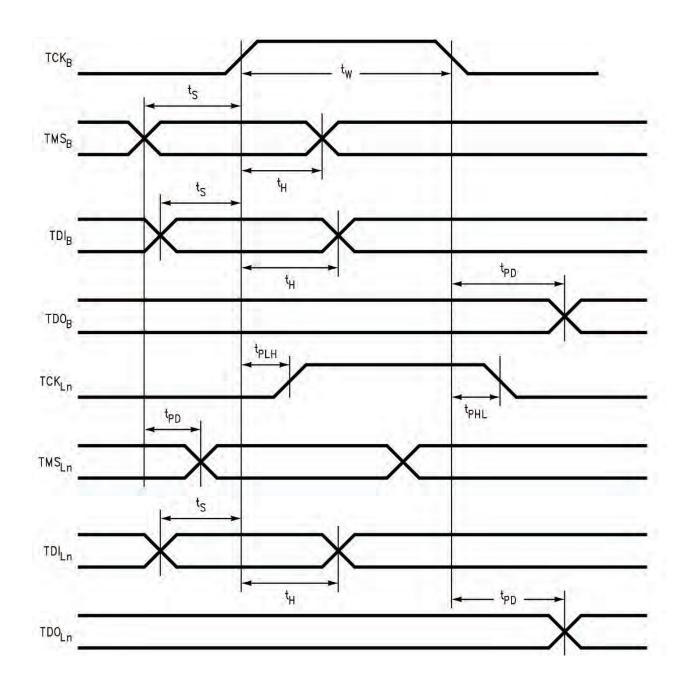

## **Timing Diagrams**

ScanBridge mode Waveforms

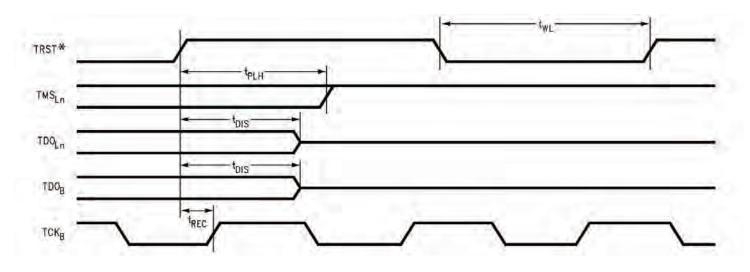

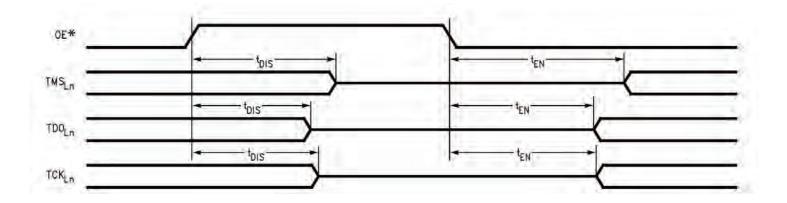

## **Timing Diagrams**

## 7 Port Multidrop IEEE 1149.1 (JTAG) Multiplexer

**Reset Waveforms**

Output Enable Waveforms

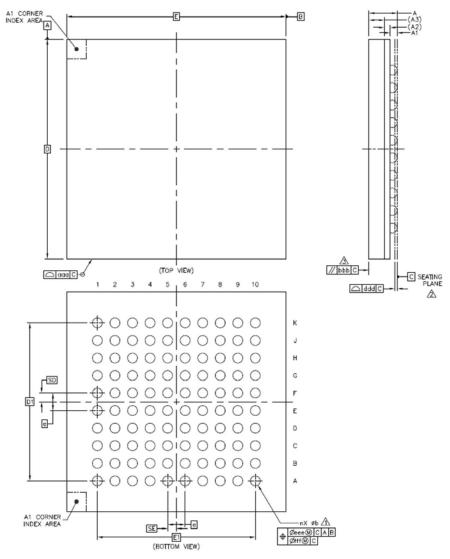

## **BGA-100 Package Dimensions**

|                             | SYMBOL | COM  | COMMON DIMENSIONS |      |  |

|-----------------------------|--------|------|-------------------|------|--|

|                             |        | MIN. | NOR.              | MAX. |  |

| TOTAL THICKNESS             | A      |      |                   | 1.4  |  |

| STAND OFF                   | A1     | 0.25 |                   | 0.4  |  |

| SUBSTRATE THICKNESS         | A2     |      | 0.26              | REF  |  |

| MOLD THICKNESS              | A3     |      | 0.7               | REF  |  |

| BODY SIZE                   | D      |      | 10                | BSC  |  |

| BODT SIZE                   | E      |      | 10                | BSC  |  |

| BALL DIAMETER               |        |      | 0.45              |      |  |

| BALL OPENING                |        |      | 0.4               |      |  |

| BALL WDTH                   | ь      | 0.4  |                   | 0.5  |  |

| BALL PITCH                  | е      |      | 0.8               | BSC  |  |

| BALL COUNT                  | n      | 100  |                   |      |  |

|                             | D1     |      | 7.2               | BSC  |  |

| EDGE BALL CENTER TO CENTER  | E1     |      | 7.2               | BSC  |  |

| DADY ADUTED TO ADUTIOT DULL | SD     |      | 0.4               | BSC  |  |

| BODY CENTER TO CONTACT BALL | SE     |      | 0.4               | BSC  |  |

| PACKAGE EDGE TOLERANCE      | 000    |      | 0.1               |      |  |

| MOLD FLATNESS               | bbb    |      | 0.2               |      |  |

| COPLANARITY                 | ddd    |      | 0.1               |      |  |

| BALL OFFSET (PACKAGE)       | eee    | 0.15 |                   |      |  |

| BALL OFFSET (BALL)          | fff    |      | 0.08              |      |  |

|                             |        |      |                   |      |  |

|                             |        |      |                   |      |  |

|                             |        |      |                   |      |  |

|                             |        |      |                   |      |  |

|                             |        |      |                   |      |  |

|                             |        |      |                   |      |  |

NOTES:

$\bigtriangleup$  DIMENSION  ${\rm b}$  is measured at the maximum solder ball diameter, parallel to datum plane c.

A DATUM C (SEATING PLANE) IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

A PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

| UNIT                  | DIMENSION AND TOLERANCES | REFERENCE DOCUMENT |       |

|-----------------------|--------------------------|--------------------|-------|

|                       |                          |                    | A4    |

| 10 X 10               | X 1.4 MM 0.8 PITCH       | SHEET              | SIZE  |

| 100 BALLS LFBGA       |                          | 98A0100MB04        | 5 A01 |

| TITLE PACKAGE OUTLINE |                          | DWG. NO.           | REV.  |

PLATING -

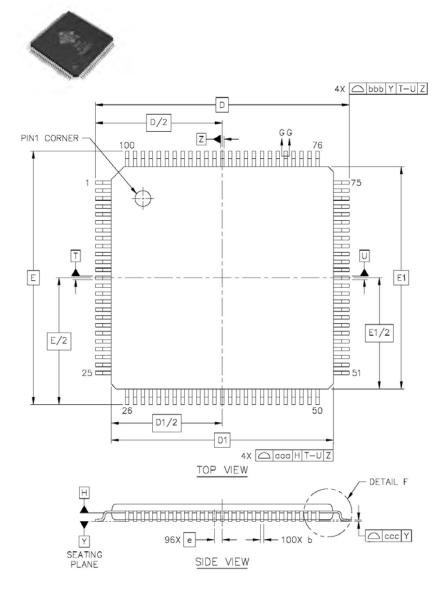

#### **TQFP-100 Package Dimensions**

← b1 ← b1 ← ddd@|Y|T-U|Z SECTION G-G

BASE METAL

#### DETAIL F

|                        |   | SYMBOL         | MIN     | NOM  | MAX  |

|------------------------|---|----------------|---------|------|------|

| TOTAL THICKNESS        |   | A              |         |      | 1.2  |

| STAND OFF              |   | A1             | 0.05    |      | 0.15 |

| MOLD THICKNESS         |   | A2             | 0.95    |      | 1.05 |

| LEAD WIDTH(PLATING)    |   | b              | 0.17    | 0.22 | 0.27 |

| LEAD WIDTH             |   | b1             | 0.17    | 0.2  | 0.23 |

| L/F THICKNESS(PLATING) |   | с              | 0.09    |      | 0.2  |

| L/F THICKNESS          |   | c1             | 0.09    |      | 0.16 |

|                        | Х | D              | 16 BSC  |      |      |

|                        | Y | E              | 16 BSC  |      |      |

| BODY SIZE              | Х | D1             | 14 BSC  |      |      |

| DOUT SIZE              | Y | E1             | 14 BSC  |      |      |

| LEAD PITCH             |   | е              | 0.5 BSC |      |      |

|                        |   | L              | 0.45    | 0.6  | 0.75 |

| FOOTPRINT              |   | L1             | 1 REF   |      |      |

|                        |   | θ              | 0.      | 3.5° | 7°   |

|                        |   | θ1             | 0*      |      |      |

|                        |   | θ2             | 11*     | 12"  | 13"  |

|                        |   | <del>0</del> 3 | 11*     | 12"  | 13"  |

|                        |   | R1             | 0.08    |      |      |

|                        |   | R2             | 0.08    |      | 0.2  |

|                        |   | S              | 0.2     |      |      |

| PACKAGE EDGE TOLERANCE |   | aaa            | 0.2     |      |      |

| LEAD EDGE TOLERANCE    |   | bbb            | 0.2     |      |      |

| COPLANARITY            |   | ccc            | 0.08    |      |      |

| LEAD OFFSET            |   | ddd            | 0.08    |      |      |

| MOLD FLATNESS          |   | eee            |         | 0.05 |      |

NOTES

- DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25MM PER SIDE. DIMENSIONS D1 AND E1 ARE MAXIMUN PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

- 2. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM & DIMENSION BY MORE THAN 0.08MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD IS 0.07MM FOR 0.4MM AND 0.5MM PITCH PACKAGES.

Notes

7 Port Multidrop IEEE 1149.1 (JTAG) Multiplexer

#### **Important Notice**

Telefunken Semiconductors PRODUCTS ARE NEITHER DESIGNED NOR INTENDED FOR USE IN MILITARY AND/OR AEROSPACE, AUTOMOTIVE OR MEDICAL DEVICES OR SYSTEMS UNLESS THE SPECIFIC TS PRODUCTS ARE SPECIFICALLY DESIGNATED BY Telefunken Semiconductors FOR SUCH USE. BUYERS ACKNOWLEDGE AND AGREE THAT ANY SUCH USE OF Telefunken Semiconductors PRODUCTS WHICH Telefunken Semiconductors HAS NOT DESIGNATED FOR USE IN MILITARY AND/OR AEROSPACE, AUTOMOTIVE OR MEDICAL DEVICES OR SYSTEMS.

Telefunken Semiconductors assumes no liability for application assistance or customer product design. Customers are responsible for their products and applications using Telefunken Semiconductors products.

Resale of Telefunken Semiconductors products or services with statements different from or beyond the parameters stated by Telefunken Semiconductors for that product or service voids all express and any implied warranties for the associated Telefunken Semiconductors product or service. Telefunken Semiconductors is not responsible or liable for any such statements.

©2011 Telefunken Semiconductors. All rights reserved. Information and data in this document are owned by Telefunken Semiconductors and may not be edited, reproduced, or redistributed in any way without written consent from Telefunken Semiconductors.

For additional information please contact support@telefunkensemi.com or visit www.telefunkensemiconductors.com